Igor Böhm

I am a Software Architect and Technical Lead at Synopsys Inc., responsible for simulation models of the DesignWare ARC EM, HS, EV, VPX DSP, as well as the new ARC-V (RISC-V) processor families. As a high level summary, I am well-known for designing a scalable, high-performance processor simulation framework, that withstood the test of time. Technical leadership of a globally dispersed team and the successful transfer of research to industry, coupled with the capability to deliver high-quality products on time, belong to a set of strengths I have been recognised for in the past.

My professional and research interests include microprocessor simulation, dynamic binary translation, microarchitecture modeling, and software architecture. Over the years, I have published some academic papers, delivered public talks, and authored some non-computer science articles.

Education

- 2012 |

PhDin Computer Science | The University of Edinburgh - 2007 |

MScin Computer Science | Johannes Kepler University Linz - 2005 |

BScin Computer Science | Johannes Kepler University Linz

Professional Experience

Software Architect and Technical Lead — Apr 2012-Present

Synopsys Inc., Munich, DE.

- Lead research and development of the DesignWare ARC nSIM processor simulation product.

- Designed and productised every ARC classic (EM, HS, EV, VPX) and RISC-V ARC-V core family in simulation.

- Built, managed, and launched the backbone of ARC HW verification based on the DesignWare ARC nSIM simulator model extended with a special purpose verification API.

- Lead productisation of NCAM, a novel, high-speed, cycle-approximate microarchitecture simulation technology.

- Integrated DesignWare ARC nSIM into high-profile Synopsys tools (e.g. Virtualizer, Platform Architect).

- Actively drive cutting edge simulator research, publishing papers in high-profile conferences (e.g. PLDI), to ensure DesignWare ARC nSIM retains its leadership position.

- Work and operate with a global team across many time zones (AMER, EMEA, APAC).

- Manage university relationships: supervise PhD students and summer internships; arrange PhD funding; draft and review legal agreements.

- Global recruitment of the best talent in an area where the required skill set is extremely hard to find.

Research Associate — Jun 2011-Dec 2011 (7 months)

The University of Edinburgh, UK.

- Research and developmenet of novel microprocessor simulation technology aimed at speeding up simulation performance whilst maintaining high-simulation detail as part of the PaStA project.

- Technology transfer and productisation of microprocessor simulation technology developed in the context of the PaStA project to Synopsys Inc.

Publications

Academic

[RAPIDO’26]Martin Kristien, Nigel Topham, Björn Franke, Igor Böhm, Harry Wagstaff, Tom Spink. “Scalable Decode Caching in Multi-Core Instruction Set Simulators,” 17th Workshop on Rapid Simulation and Performance Evaluation for Design Optimization: Methods and Tools, January 2026. https://doi.org/10.1109/TCAD.2020.3013048[CASES’20]Martin Kristien, Tom Spink, Brian Campbell, Susmit Sarkar, Ian Stark, Björn Franke, Igor Böhm, Nigel Topham. “Fast and Correct Load Link/Store Conditional Instruction Handling in DBT Systems,” International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, September 2020. https://doi.org/10.1145/3787501.3787504[VEE’19]Martin Kristien, Tom Spink, Harry Wagstaff, Björn Franke, Igor Böhm, Nigel Topham. “Mitigating JIT Compilation Latency in Virtual Execution Environments,” Proceedings of the 15th ACM SIGPLAN/SIGOPS International Conference on Virtual Execution Environments, April 2019. https://doi.org/10.1145/3313808.3313818[IJPP’12]Oscar Almer, Igor Böhm, Tobias Edler von Koch, Björn Franke, Stephen Kyle, Volker Seeker, Christopher Thompson, Nigel Topham. “A Parallel Dynamic Binary Translator for Efficient Multi-Core Simulation,” International Journal of Parallel Programming, September 2012. https://doi.org/10.1007/s10766-012-0222-9[LCTES’12]Stephen C Kyle, Igor Böhm, Björn Franke, Hugh Leather, Nigel Topham. “Efficiently Parallelizing Instruction Set Simulation,” Proceedings of the 13th ACM SIGPLAN/SIGBED International Conference on Languages, Compilers, Tools and Theory for Embedded Systems, May 2012. Received HiPEAC Paper Award. http://dx.doi.org/10.1145/2248418.2248422[IC-SAMOS’11]Oscar Almer, Igor Böhm, Tobias Edler von Koch, Björn Franke, Stephen Kyle, Volker Seeker, Christopher Thompson, Nigel Topham. “Scalable Multi Core Simulation Using Parallel Dynamic Binary Translation,” Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation, Samos, Greece, July 19-22, 2011. http://dx.doi.org/10.1109/SAMOS.2011.6045461[PLDI’11]Igor Böhm, Tobias Edler von Koch, Björn Franke, Nigel Topham. “Generalized Just-In-Time Trace Compilation using a Parallel Task Farm in a Dynamic Binary Translator,” Proceedings of the International Conference on Programming Language Design and Implementation, June, 2011. Received HiPEAC Paper Award. https://doi.org/10.1145/1993498.1993508[HiPEAC’11]Igor Böhm, Björn Franke, Nigel Topham. “Cycle Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator,” Transactions on High-Performance Embedded Architectures and Compilers: Volume 5, Issue 4, Springer, 2011. https://groups.inf.ed.ac.uk/pasta/pub_HIPEAC_2011_ISS_CYCLE_BOHM.html[IC-SAMOS’10]Igor Böhm, Björn Franke, Nigel Topham. “Cycle Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator,” Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation, Samos, Greece, July 19-22, 2010. Received Best Paper Award. http://dx.doi.org/10.1109/ICSAMOS.2010.5642102[CGO’10]Tobias Edler von Koch, Igor Böhm, Björn Franke, Nigel Topham. “Integrated instruction selection and register allocation for compact code generation exploiting freeform mixing of 16- and 32-bit instructions,” Proceedings of the 8th annual IEEE/ACM International Symposium on Code Generation and Optimization, Toronto, Canada, April, 2010. http://dx.doi.org/10.1145/1772954.1772980

White Papers

[2021.03]Igor Böhm, Alexander Chuykov. “Fast Cycle Approximate Simulation Using ARC nSIM NCAM”.[2021.01]REF-2021. “Research Excellence Framework Impact Case Study—Two Billion Dwevices enabled annually by optimised low power embedded processor”.[2017.04]Igor Böhm. “Speed, Accuracy, and Visibility—Instruction Set Simulation without compromise!”.

Theses

[PhD’13]Igor Böhm. “Speeding up dynamic compilation: concurrent and parallel dynamic compilation,” PhD Thesis, July 2013. https://era.ed.ac.uk/handle/1842/6694[MSc’07]Igor Böhm. “Automatic Code Generation using Dynamic Programming Techniques,” MSc Thesis, July 2007. https://9lab.org/pub/papers/hburg07.pdf

Books

[BOOK’08]Igor Böhm. “Automatic Code Generation using Dynamic Programming,” VDM Verlag Dr. Müller, ISBN-10: 9783836461580 ASIN: 3836461587, January 17, 2008. https://www.amazon.com/dp/3836461587/

Awards

[RAPIDO’26]Best Paper Award: “Scalable Decode Caching in Multi-Core Instruction Set Simulators”, issued by HiPEAC, Feb 2026.[LCTES’12]HiPEAC Paper Award: “Efficiently Parallelizing Instruction Set Simulation”, issued by HiPEAC, Jan 2012.[PLDI’11]HiPEAC Paper Award: “Generalized Just-In-Time Trace Compilation using a Parallel Task Farm in a Dynamic Binary Translator”, issued by HiPEAC, Jan 2011.[IC-SAMOS’10]Best Paper Award: “Cycle Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator”, issued by IEEE, Jan 2011.[HiPEAC]Best Poster Award: “The EnCore Microprocessor”, issued by HiPEAC.

Supervised PhD Students

[PhD’24]Martin Kristien. “Efficient cross-architecture simulation of multicore systems,” PhD Thesis, October 2024. https://era.ed.ac.uk/items/b7045385-36f1-4f28-b9d8-66a2446987f9

Interests

- Microprocessor Simulation

- Dynamic Binary Translation

- Computer Architecture

- Software Architecture

- Functional Programming

- Metaprogramming

- Political Science and Commentary

- The Plan Fell Off

Recommendations

“Igor has been a star software engineer, from his time at the University of Edinburgh and at Synopsys. He has three traits that combined, make him a stellar contributor. As an innovator, he developed and championed key processor instruction set technology, taking his research through multiple generations of successful product adoption and use. As a software engineer, he is highly effective working with customers in challenging technical engagements, as well as driving internal teams to achieve high standards via process and camaraderie. And personally, he is enthusiastic and passionate and was a source of energy and vision for me throughout our decade together. Highly recommended.” — Bob Gable

](/img/cv/MiteshShah-Recommendation.png)

LinkedIn recommendation by Mitesh Shah

“Igor is a real deal. I hired him as an intern while he was doing his doctorate at University of Edinburgh and it was clear from the start he was going to be a superstar performer. We started the whole new simulation technology framework and the new team based on the research he was doing in the University and in no time we were able to release a product based on the new state of the art simulation technology with 10x perf increase, surpassing and replacing the existing solution in no time. That is still one of the proudest moments of my professional career too. Since then he continued to tech-lead to deliver new quarterly releases packed with many customer requested features and fundamental perf related wins time and again. I am so grateful to have supported him and the simulation team to achieve some amazing success together. He tech-leads the team from the front and is very good at providing useful directions. He is a powerhouse of interesting ideas and projects, to date I cherish many of the passionate brainstorming and discussions that we had during my time at Synopsys. He is passionate about highest code quality standards and provides guidance through extensive code reviews. He strives to maintain the continuity of the overall systems design. He is good at bringing complicated projects to successful completion, and visualizing the steps, tools and techniques that would get us there. He is a very good mentor for his peers and believes in strong team building. He strived to set up proper systems and guidance in place to accelerate on-boarding of new members which became exemplary in the org. I am so glad that I got an opportunity to channelize his passion and drive towards some great new product releases and customer success. I wish him all the success in the future and keep that fire burning, I am sure you will achieve even greater heights in your career.” — Mitesh Shah

LinkedIn recommendation by Stephen Henry

“From my experience in this industry, one seldom finds an individual that combines the highest level of ability with such great enthusiasm. Igor is one such individual. His project at Synopsys is something I have subsequently seen replicated at other companies by multiple individuals but at a far lower degree of sophistication. He is an incredibly motivating individual and a first-rate engineer. I would have no hesitation whatsoever in providing my highest level of recommendation.” — Stephen Henry

Software

Some scripts, tools, and software of mine are hosted here:

- GitHub: https://github.com/1g0rb0hm/

- Shithub: https://shithub.us/igor/

- Sourcehut: https://git.sr.ht/~ig0r/

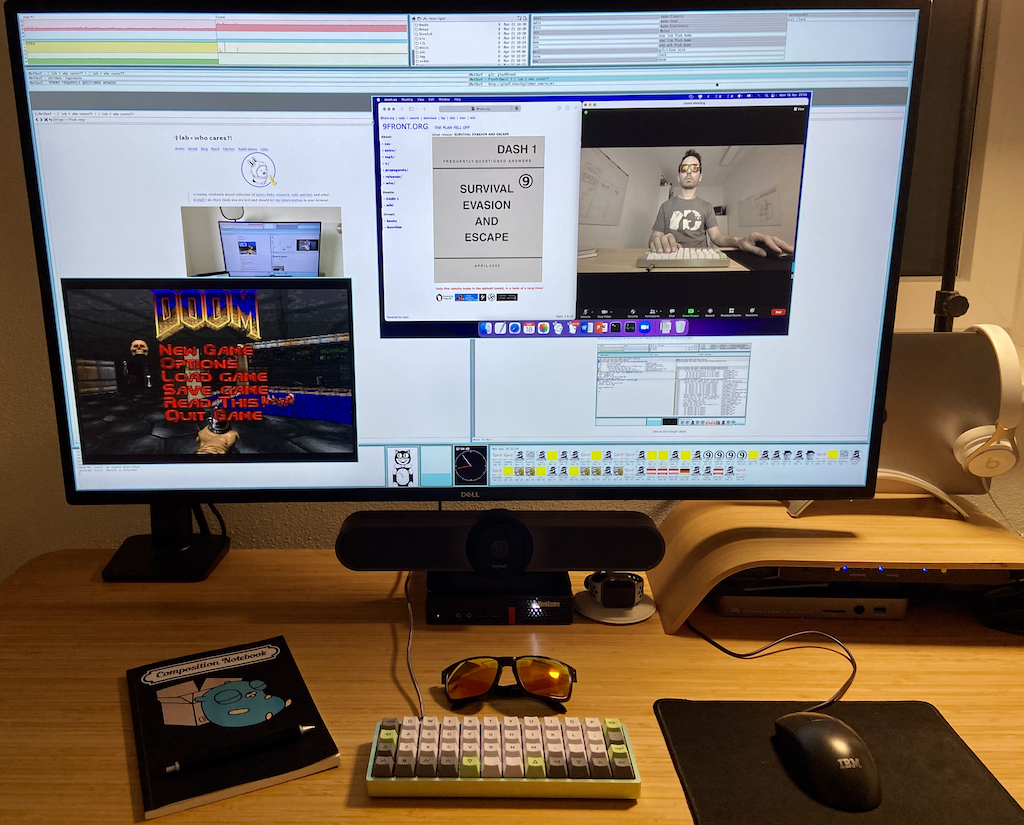

⑨ lab ≡ cockpit ≡ Lenovo ThinkCentre M910Q tiny…