Note/nSIM NCAM — Instruction Set Simulation

Publications

White Papers

[2021.03]Igor Böhm, Alexander Chuykov. “Fast Cycle Approximate Simulation Using ARC nSIM NCAM”.[2017.04]Igor Böhm. “Speed, Accuracy, and Visibility - Instruction Set Simulation without compromise!”.

Research Impact

[2021.01]REF-2021. “Research Excellence Framework Impact Case Study—Two Billion Dwevices enabled annually by optimised low power embedded processor”.

PhD Theses

[PhD’24]Martin Kristien. “Efficient cross-architecture simulation of multicore systems,” PhD Thesis, October 2024. https://era.ed.ac.uk/items/b7045385-36f1-4f28-b9d8-66a2446987f9[PhD’15]Harry Wagstaff. “From high level architecture descriptions to fast instruction set simulators,” PhD Thesis, November 2015. https://era.ed.ac.uk/items/5ad3c9b8-60f5-49dc-b779-7862fbd135ba[PhD’13]Igor Böhm. “Speeding up dynamic compilation: concurrent and parallel dynamic compilation,” PhD Thesis, July 2013. https://era.ed.ac.uk/handle/1842/6694

Research

[RAPIDO’26]Martin Kristien, Nigel Topham, Björn Franke, Igor Böhm, Harry Wagstaff, Tom Spink. “Scalable Decode Caching in Multi-Core Instruction Set Simulators,” 17th Workshop on Rapid Simulation and Performance Evaluation for Design Optimization: Methods and Tools, January 2026. https://doi.org/10.1109/TCAD.2020.3013048[CASES’20]Martin Kristien, Tom Spink, Brian Campbell, Susmit Sarkar, Ian Stark, Björn Franke, Igor Böhm, Nigel Topham. “Fast and Correct Load Link/Store Conditional Instruction Handling in DBT Systems,” International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, September 2020. https://doi.org/10.1145/3787501.3787504[VEE’19]Martin Kristien, Tom Spink, Harry Wagstaff, Björn Franke, Igor Böhm, Nigel Topham. “Mitigating JIT Compilation Latency in Virtual Execution Environments,” Proceedings of the 15th ACM SIGPLAN/SIGOPS International Conference on Virtual Execution Environments, April 2019. https://doi.org/10.1145/3313808.3313818[IJPP’12]Oscar Almer, Igor Böhm, Tobias Edler von Koch, Björn Franke, Stephen Kyle, Volker Seeker, Christopher Thompson, Nigel Topham. “A Parallel Dynamic Binary Translator for Efficient Multi-Core Simulation,” International Journal of Parallel Programming, September 2012. https://doi.org/10.1007/s10766-012-0222-9[LCTES’12]Stephen C Kyle, Igor Böhm, Björn Franke, Hugh Leather, Nigel Topham. “Efficiently Parallelizing Instruction Set Simulation,” Proceedings of the 13th ACM SIGPLAN/SIGBED International Conference on Languages, Compilers, Tools and Theory for Embedded Systems, May 2012. Received HiPEAC Paper Award. http://dx.doi.org/10.1145/2248418.2248422[IC-SAMOS’11]Oscar Almer, Igor Böhm, Tobias Edler von Koch, Björn Franke, Stephen Kyle, Volker Seeker, Christopher Thompson, Nigel Topham. “Scalable Multi Core Simulation Using Parallel Dynamic Binary Translation,” Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation, Samos, Greece, July 19-22, 2011. http://dx.doi.org/10.1109/SAMOS.2011.6045461[PLDI’11]Igor Böhm, Tobias Edler von Koch, Björn Franke, Nigel Topham. “Generalized Just-In-Time Trace Compilation using a Parallel Task Farm in a Dynamic Binary Translator,” Proceedings of the International Conference on Programming Language Design and Implementation, June, 2011. Received HiPEAC Paper Award. https://doi.org/10.1145/1993498.1993508[HiPEAC’11]Igor Böhm, Björn Franke, Nigel Topham. “Cycle Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator,” Transactions on High-Performance Embedded Architectures and Compilers: Volume 5, Issue 4, Springer, 2011. https://groups.inf.ed.ac.uk/pasta/pub_HIPEAC_2011_ISS_CYCLE_BOHM.html[IC-SAMOS’10]Igor Böhm, Björn Franke, Nigel Topham. “Cycle Accurate Performance Modelling in an Ultra-Fast Just-In-Time Dynamic Binary Translation Instruction Set Simulator,” Proceedings of the International Symposium on Systems, Architectures, Modeling, and Simulation, Samos, Greece, July 19-22, 2010. Received Best Paper Award. http://dx.doi.org/10.1109/ICSAMOS.2010.5642102

Talks

Demos and Screencasts

Simulation Speed

Reducing dynamic compilation latency by exploiting concurrent and parallel dynamic compilation:

Interpreter vs. JIT

Benefit of nSIM JIT (aka TURBO) based on a state-of-the-art concurrent JIT compiler to speed-up instruction accurate simulation of audio and video codecs:

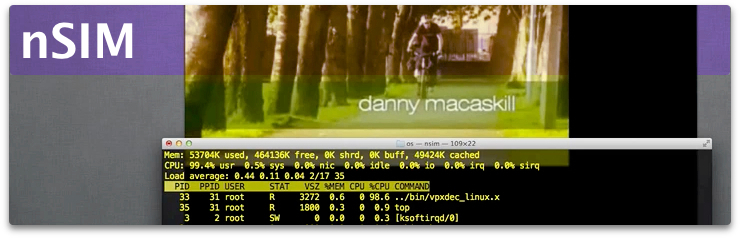

VP8 Decoding and Playback

Benefit of nSIM JIT based on a state-of-the-art concurrent JIT compiler to speed-up instruction accurate simulation of audio and video codecs running inside a simulated Linux OS image:

Concurrent Multicore Simulation

8 Cores running dithering algorithm and drawing an image per core to a virtual screen device. The first run is executed in interpretive mode, the second is using a concurrent and parallel dynamic compiler to speed up simulation: